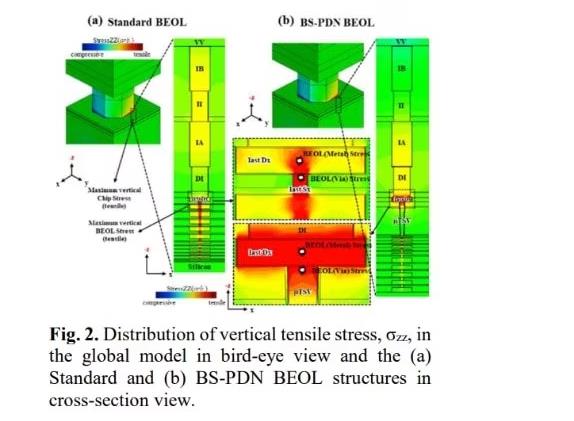

Companies such as Samsung Electronics and Intel are actively deploying backside power supply network technology (BSPDN), and plan to apply this technology in future chip manufacturing processes. BSPDN is a design structure that improves power and signal lines by arranging power wiring on the backside of the wafer. Compared with the traditional front-end power supply network (FSPDN), the arrangement sequence of BSPDN is signal line-transistor-power line, which can provide better performance and cost-effectiveness.

Samsung Electronics recently announced its BSPDN research results, which is the first time they have disclosed specific research results related to BSPDN. According to the research of Samsung Electronics, the application of BSPDN can reduce the processor area by 14.8%, and can increase the number and performance of transistors inside the chip. In addition, BSPDN can also reduce the wiring length and improve the performance of the chip.

Intel also announced its backside power supply technology called "PowerVia", and plans to apply it in its 20A process technology. According to Intel's test results, PowerVia can improve power supply and signal transmission, and increase the chip's cell density and utilization. Tests also showed that PowerVia can reduce platform voltage and increase frequency.

In order to apply BSPDN, chemical mechanical polishing (CMP) technology and TSV technology for connecting signal lines to power lines are very important. TSMC plans to mass-produce the 2nm process in 2025, and plans to launch the N2P process with backside power supply technology in 2026.

Although Samsung Electronics has not disclosed specific implementation plans, they are currently perfecting the second-generation SF3 manufacturing technology based on 3nm-level gate-around transistors, and plan to achieve mass production in 2024. Samsung also plans to launch SF3P and 2nm-class SF2 processes in 2025, and may implement BSPDN technology in these processes.

Generally speaking, the introduction of BSPDN technology will bring better performance and cost-effectiveness to the chip manufacturing industry. Companies such as Samsung Electronics and Intel are actively developing and applying this technology, bringing more possibilities for future chip manufacturing processes.

We are the professional distributor of electronic components, providing a large variety of products to save you a lot of time, effort, and cost with our efficient self-customized service. careful order preparation fast delivery service。

Recommended by Samsung Electro-Mechanics:

- Arrays/Networks Resistors

- Capacitor Networks, Arrays

- Ceramic Capacitors

- Chip Resistors-Surface Mount

- Ferrite Beads and Chips

- Fixed Inductors

- Tantalum - Polymer Capacitors

Articles you may be interested in:

The market recovery is not as good as expected, and the news is that Qualcomm's inventory chips will cut prices,

The United States announces investment restrictions on China, targeting three areas of chips, AI and quantum technology

Summary of 14 topology calculation formulas for switching power supplies

Semiconductor giants team up to lay out the "third" architecture: the era of RISC-V architecture is accelerating

Save billions of dollars, Apple only pays for TSMC's 3nm premium chips

Ex-Samsung exec urges U.S. to abandon chip strategy with China